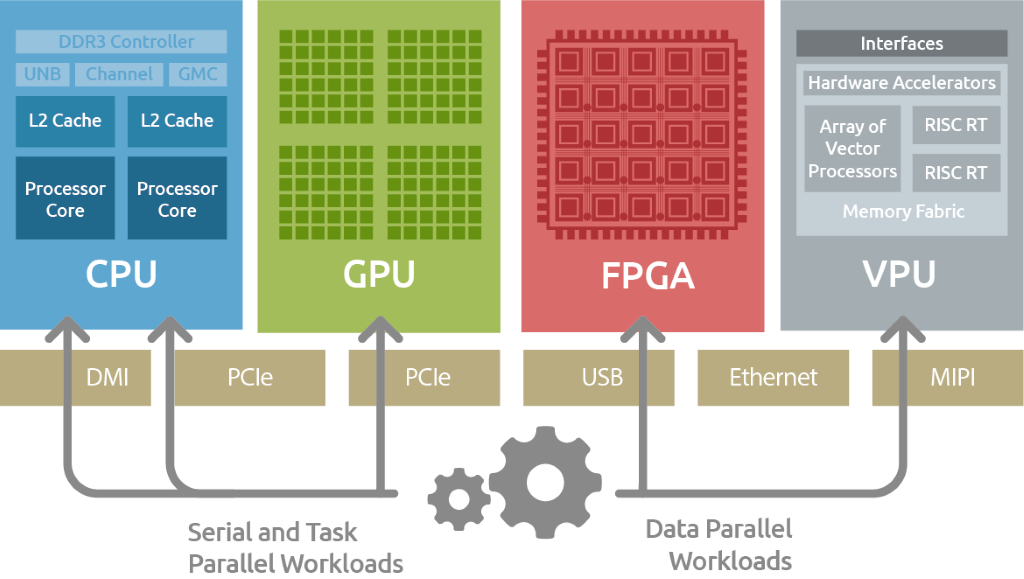

自21世纪初正式创立以来,PCI Express(PCIe)接口就成为了数据中心和计算应用中芯片间数据传输的行业标准。GPU、FPGA和TPU等特定加速卡都是通过PCIe接口与各个计算节点快速传输数据。

不同芯片之间的业务流数据通过PCIe接口传输

图源:ADLINK

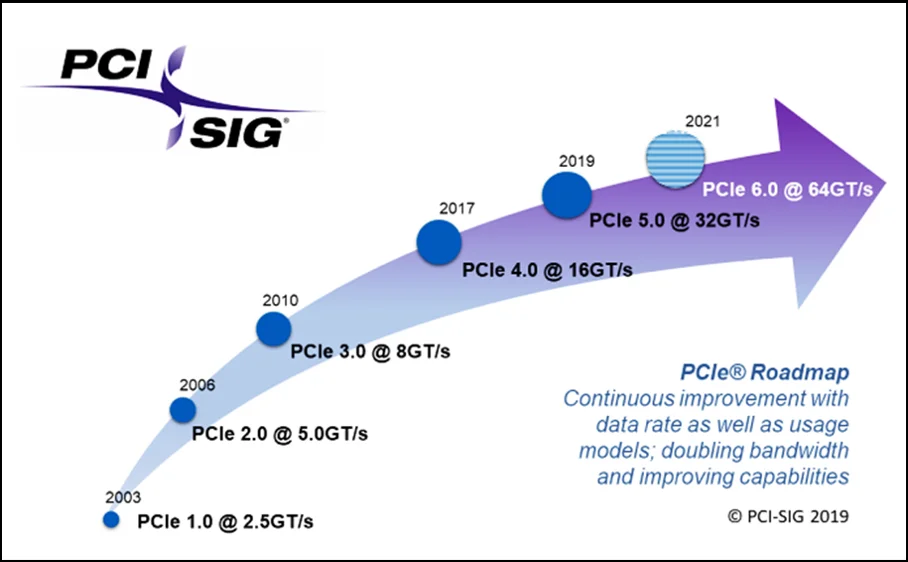

自2015年以来,全球数据流量猛增。随着数据中心转向100G以太网甚至更高,服务器和网络设备中的 PCIe互连成为瓶颈。下图展示了PCIe标准的演进趋势,可以看出PCIe 2.0到3.0/4.0,分别花费了5年和7年的时间。但是PCIe 4.0到5.0,再到6.0,时间间隔却分别只有2年和3年,而且PCIe 6.0 64GT/s的传输速度也是3.0标准的8倍。

PCIe性能加速曲线

PCIe 6.0 规范支持数据中心向800G以太网的切换,800 Gb/s所需的带宽为100 GB/s,在x16 PCIe 6.0链路配置下,单向带宽可以达到128 GB/s,在多个端口做链路聚合之后,完全支持1.6T 以太网的带宽需求。

NVLink专注于Nvida的GPU间数据交换,满足大规模并行处理和AI模型训练等高性能计算任务的带宽需求。而PCIe则凭借其开放性和广泛的兼容性,迅速适应市场变化和技术演进。

PCIe 6.0提供了高达64 GT/s的单向传输速率,显著提高了数据吞吐量。在能效方面,PCIe 6.0采用了PAM-4,以优化功耗和信号完整性。因此,PCIe 6.0成为多GPU显卡互联的首选。

CXL 3.0基于PCIe 6.0协议,CXL内存池共享技术支持跨 CPU、GPU、FPGA 等设备的内存统一编址,可将分散的内存聚合为共享池,动态分配给不同任务。通过CXL连接的内存扩展卡,单服务器内存容量可从TB 级提升至PB级,突破大模型训练的内存限制,同时减少采购高价HBM。

NVMe(Non-Volatile Memory Express)是一种专为固态硬盘(SSD)设计的存储协议,旨在充分利用 PCIe总线的高速带宽,提供高性能、低延迟的存储解决方案。PCIe 6.0 为 NVMe 存储设备提供了更高的带宽和更低的延迟,显著提升了存储性能和能效,为数据存储提供高速、低延迟的存储方案。

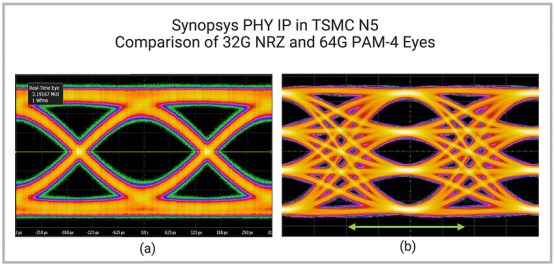

PCIe 5.0使用传统的NRZ(Non-Return-to-Zero)调制方式,当数据速率达到32GT/s时,奈奎斯特频率也达到16GHz,频率升高带来的损耗与耦合噪声和串扰的增加,使得PCIe 5.0信道成为最难处理的NRZ信道。

PCIe 6.0使用PAM-4调制,PAM-4使用四个信号电平(0, 1, 2, 3),形成三个“眼”(eye),每个电平对应两位数据。这种多电平调制方式显著提高了数据传输效率。

PCIe 5.0的单眼眼图与PCIe 6.0的3眼眼图

PCIe 5.0和PCIe 6.0的信号奈奎斯特频率都是16GHz,但是PAM-4的四个电压电平在一个UI中使用2bit编码,而NRZ是1bit编码,因此使数据速率提高了一倍。

由于发射端(TX)的总体电压摆幅没有增加,PAM-4每只眼的可用电压仅为NRZ的1/3。因此,信号对噪声更加敏感,对于在TX和RX之间信号完整性的要求更高。从NRZ信号转换为PAM-4信号,对于信号抖动的要求要提高2倍,同时会导致信噪比(SNR)退化9.6dB,因此封装和PCB中的串扰和回波损耗也比PCIe 5.0高。

噪声敏感性增加意味着我们用于PCIe的1e-12误码率(BER)不可行,并且需要前向纠错 (FEC),因为PAM-4信令的BER将比1e-12高几个数量级,第一位误码率(FBER)的目标是1e-6。前向纠错 (FEC) 弥补了这种性能上的不足。PCIe 6.0规范将额外的FEC延迟限制为2 纳秒或更短。为了将链路重试几率保持在较低水平,FEC和CRC(循环冗余校验)需要协同工作。

因此PCIe 6.0采用了256字节FLIT作为标准大小的数据传输单元,为了支持FEC的固定数据包大小要求,PCIe 6.0 包含基于流控制单元 (FLIT) 的编码。通过消除在物理层对数据包进行分组的必要性,此修改还简化了数据管理程序,降低了延迟并提高了效率。

PCIe 6.0引入了一种新的低功耗状态,称为L0p,允许PCIe 6.0链路在不中断数据流的情况下扩展带宽利用率,从而降低功耗。在前几代中,为了改变链路宽度,整个链路重新训练时,流量会中断几微秒,但L0p允许链路关闭通道,从而降低功耗,同时始终保持至少一个通道处于活动状态,即使其他通道正在进行链路训练。需要注意的是,这种新的低功耗模式仅在FLIT模式下可用,而L0s支持非FLIT模式。

这种新的低功耗模式是对称的,这意味着TX和RX一起缩放,并且支持FLIT模式的重定时器也支持这种模式。在处于L0p期间空闲通道的PHY功耗预计与关闭通道时的功耗相近。

由于PCIE 6.0使用了PAM4信号制式,在36 dB损耗链路下,是无法达到1E-06误码率要求的。因此,PCIe 6.0规范不得不将整个物理通道的总损耗值降低到32 dB。

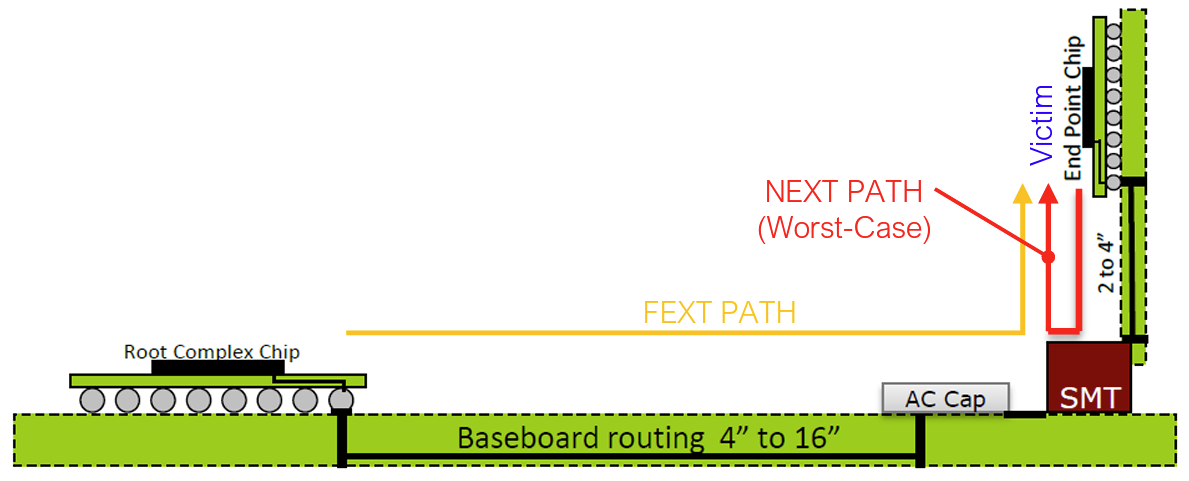

PCIe信号传输链路示意图

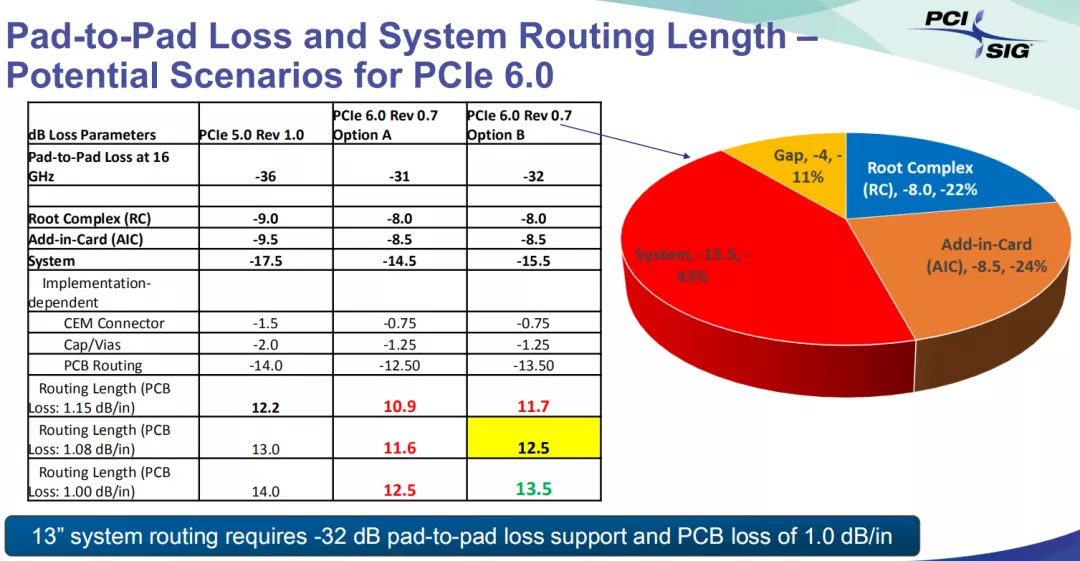

如上图PCIe信号的传输链路典型图示,PCIe卡通过CEM连接器与主板上的芯片建立起来信号传输通道。因此在信号传输的过程中会产生PCB走线损耗、封装损耗、连接器损耗、过孔损耗等。PCIe 6.0规范对于各个部分的损耗要求如下:

PCIe6.0 规范对于传输损耗的要求

如上图PCIe 6.0规范所示,对于PCB所产生的最大损耗不能超过13.5dB,只有PCB的损耗达到1.00dB/inch的时候,走线长度才能达到常规的13.5inch长度。

现阶段,PCIE 4.0 16GT/s的速率,主板已经要使用Megtron 4/Megtron 6板材,考虑到CPU芯片的尺寸在不断增大,在PCIE 5.0和PCIE 6.0时代,主板PCB板材需要进一步提升到Megtron 6/Megtron 7等级。铜箔类型需优选HVLP(低粗糙度)以上等级,以减少信号因趋肤效应产生的损耗。