嵌入式核心板又叫SOM(Systems-on-Module)板,核心板集成了CPU和各种外设,如内存(DDR)、存储(eMMC或FLASH)、电源管理(PMIC)、晶振等。同时引出如USB、GPIO、SPI、I2C、UART、以太网、PCIe等各种接口,以满足各种应用的需求。

核心板一般采用板对板连接器、邮票孔焊接、金手指、COM Express等形式与底板连接,并且通常将CPU的所有功能引脚或大部分功能引脚引出,用户在设计产品时只需根据应用场景进行功能接口的电路设计,从而降低了硬件开发难度,节省了开发时间。

Intel Atom x6000E COM Express核心板

来自:Congatec

SOM适用于包括工业自动化、医疗设备、汽车电子、通信系统和物联网(IoT)在内的多种行业。使用SOM,可以大大缩短产品开发周期,降低综合成本,提高产品的可靠性。

为了确保嵌入式核心板硬件和软件的兼容性、模块化和可扩展性。不同组织或公司定义了多个标准,常见的嵌入式核心板标准如下:

Open Standard Module (OSM)

OSM核心板是一个可焊接的LGA封装模块,尺寸紧凑,最大的尺寸为45mm x 45mm,模块功率通常在15W以下。对于物联网应用十分友好,可以满足低成本和日益增长的性能需求。

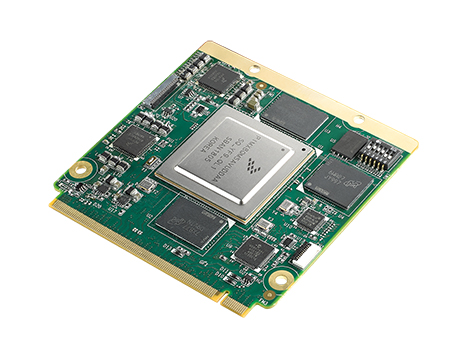

OSM标准的IMX8MP 核心板

来自:ADLINK

QSeven (Q7)

由NXP Semiconductors(原Freescale Semiconductor)推出的一种基于ARM架构的嵌入式处理器模块标准。标准采用230-pin MXM金手指设计, 便于手持设备、HMI和标牌应用中的高速I/O连接。

基于NXP i.MX 8QM Qseven 核心板

来自:Advantech

SMARC

SMARC (Standard Module Advanced RISC Computer),是一种用于定义ARM架构的嵌入式计算机模块的开放标准。采用314针的MXM金手指连接器,适用于高性能和低功耗要求的产品。

Intel Atom x7000 series (Amston Lake) 核心板

来自:ADLINK

COM Express

由PICMG(PCI Industrial Computer Manufacturers Group)定义的一种模块化计算机标准,支持多种处理器架构,如x86、ARM和PowerPC。COM Express模块包括Mini、Basic和Compact三种尺寸,可以针对特定的应用和功率来选择适合的尺寸。

为了适应下一代AIoT应用,COM Express R3.1新增了多个高级接口支持包括Type 6/7/10新增PCIe Gen 4接口,Type 6模块增加USB 4.0接口,Type 7模块新增第二个PCIe Clock,并将10G以太网升级至支持CEI边带信号。

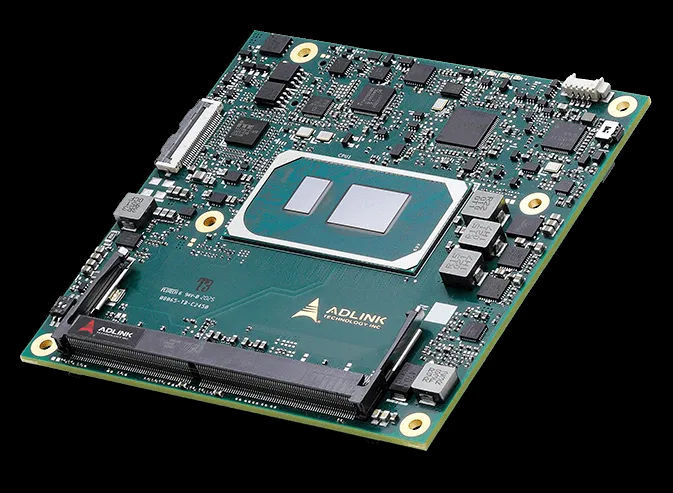

COM Express Type 6 第11代 Intel Cor i7 核心板

来自:ADLINK

随着嵌入式处理器的性能越来越高,内存速率越来越快,嵌入式核心板的PCB层数也从早期的4层发展到了8-12层,由于支持越来越多的高速接口,对板材损耗的要求也越来越高。

一般遵循以下步骤进行嵌入式核心板PCB的设计:

确定元器件布局

一般来讲,核心板标准要求里已经规定了标准的外型和接口,元器件的布局变化不会很大。一般思路是按照CPU的参考手册要求,遵循最优的fanout布局设计,确定CPU、DDR和Flash的布局,再优化电源和周围器件的布局。

确定板厚

常规的PCB成品厚度为0.5mm、0.8mm、1.0mm、1.2mm、1.6mm、2.0mm、3.2mm、6.4mm等等。一般在核心板的设计标准里会规定板厚,设计时需遵循相应的要求,对于没有规定要求的,从结构可靠性角度可以做厚一些。

确定PCB层数和划分功能层

确定总层数和划分信号层、电源层和地层,需要从系统性的角度综合考虑,是一个相互妥协的结果。首先需要确定层数能够满足布线的需求,其次需要满足高速信号线的布线要求,最后考虑电源完整性、EMC和热设计的要求。在满足功能的前提下,尽量压缩PCB的层数。

确定内外层铜厚

叠层设计时必须平衡铜箔的厚度,使电源/地平面层铜的厚度满足载流要求。3oz以上属于厚铜,常用于高压、大电流的电力电子产品。

对于信号层铜的厚度来讲,线宽/线距较小,需要铜尽可能薄才能满足精确的蚀刻的要求。高速信号线由于趋肤效应的影响,电流只在铜箔表面附近流动,更厚的铜箔并不会带来更好的性能。所以内层信号层的铜厚通常为Hoz,即0.5盎司。

确定阻抗线的分布

核心板上的高速接口信号线都有阻抗要求,常见的单端50Ω、差分100Ω等。阻抗控制,需要有参考平面,走线的铜厚、介电常数、线宽、线距都会影响阻抗。在设计时阻抗线时,在满足阻抗要求的前提下,尽量压缩阻抗线出现的层数。

EDA工具都支持阻抗计算,可以按照设计的叠层结构,去调整走线的参数。

确定过孔结构

大多数核心板由于高密度的属性,都会使用盲孔和埋孔来优化布线空间,盲孔和埋孔也同时造成了PCB需要多次压合增加了工序,PCB的制造难度上升,因此也更加昂贵。

在叠层设计时,需要在满足设计的前提下,尽量简化孔的结构。

选择满足设计要求的板材、PP和铜箔

FR-4能够满足大多数PCB的需求,价格便宜而且电气性能良好,高速PCB会选用高速板材,比如松下的Megtron4/6等,高速PCB需要选择具有最低损耗角正切和较小介电常数的介电材料,来满足高速信号对于损耗的要求。

铜箔粗糙度(铜牙)使线路的宽度、线间距不均匀,从而导致阻抗不可控,同时由于趋肤效应,电流集中在导体的表层,铜箔的表面粗糙度影响信号传输的长度。信号的频率在5GHz以下时铜箔粗糙度的影响不是太明显,大于5GHz时铜箔粗糙度的影响开始越来越大,在大于10Ghz的高速信号的设计时尤其需要重视。