随着AI对更强大计算的需求增加,以及半导体行业进入在封装中使用多个“Chiplet”的异构时代,封装更加复杂和精密,对信号传输速度、功率传输、设计规则和封装基板稳定性的改进将至关重要。

晶圆级封装(Wafer Level Packaging,缩写WLP)是一种先进的封装技术,与打线型(Wire-Bond)和倒装型(Flip-Chip)封装技术相比 ,能省去打金属线、外延引脚(如QFP)、基板或引线框等工序。

晶圆级封装具有以下优点:

封装尺寸小

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

高传输速度

与传统金属引线产品相比,WLP一般有较短的连接线路,在高速和高频情况下,表现较好。

高密度连接

WLP可运用数组式连接,芯片和电路板之间连接不限制于芯片四周,提高单位面积的连接密度。

生产周期短

WLP从芯片制造到、封装到成品的整个过程中,中间环节大大减少,生产效率高,周期缩短很多。

工艺成本低

WLP是在硅片层面上完成封装测试的,以批量化的生产方式达到成本最小化的目标。

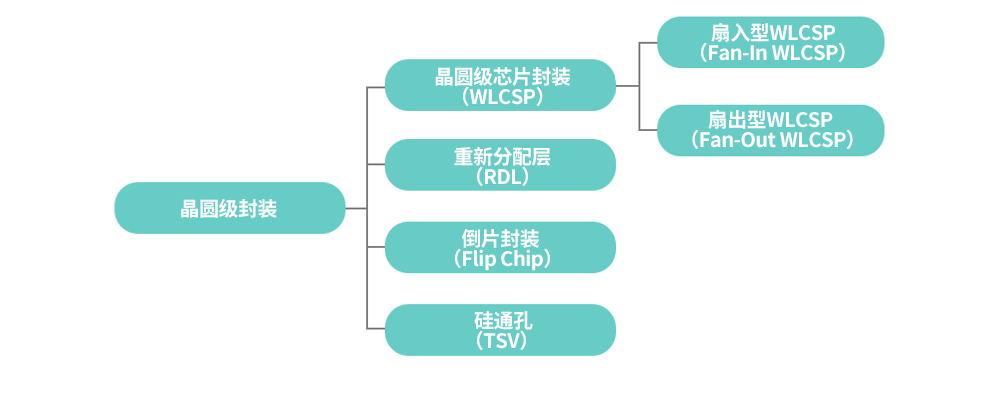

晶圆级封装方法可分为四种不同类型:

晶圆级芯片封装(WLCSP)

可直接在晶圆顶部形成导线和锡球(Solder Balls),无需基板。

重新分配层(RDL)

使用晶圆级工艺重新排列芯片上的焊盘位置1,焊盘与外部采取电气连接方式。

倒片(Flip Chip)封装

在晶圆上形成焊接凸点2进而完成封装工艺。

硅通孔(TSV)封装

通过硅通孔技术,在堆叠芯片内部实现内部连接。

晶圆级封装的分类

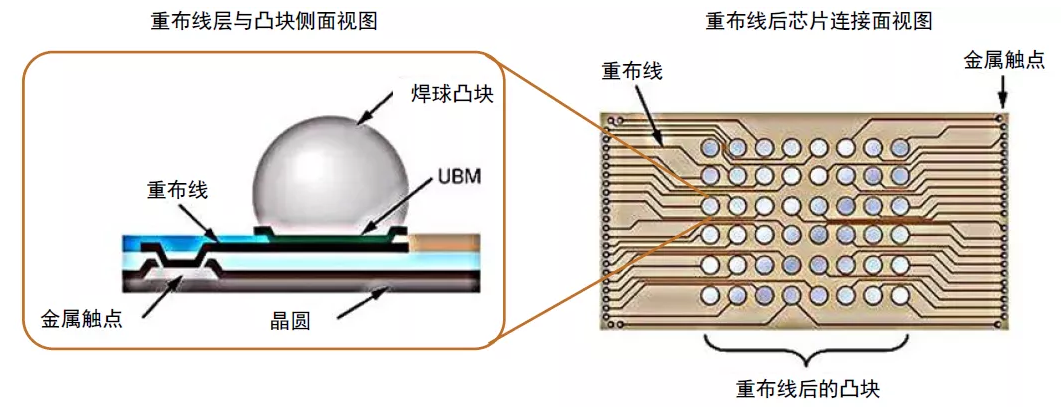

RDL的全称是(ReDistribution Layer)重布线层,RDL重布线层作为晶圆级封装中的核心技术,起着XY平面电气延伸和互联的作用。RDL是将原来设计的芯片线路接点位置(I/O pad),通过晶圆级金属布线制程和凸块制程改变其接点位置,使芯片能适用于不同的封装形式。

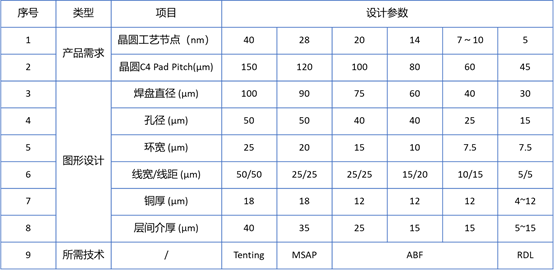

基于明阳在半导体领域的布局,先进封装载板与测试板进行工艺技术研发。

当前工艺主要分为tenting,mSAP,SAP三种,Tenting制程由于蚀刻工艺的限制, 通常难以制作线宽/线距小于30/30μm的线路,mSAP制程的是在超薄铜箔上进行线路铜的加厚,随后通过闪蚀工得到完整的导电线路。具有制作线宽/线距小至25/25μm及以下的产品的能力,SAP流程与MSAP类似,但底铜更薄,可制作15/20μm的产品。

RDL技术可以制作更小的线路,调整阵列排布,是未来半导体领域重点技术之一。RDL技术相较于MSAP/SAP工艺的优点是将钻孔转为光刻成孔,具备更高精度,可以制作更小的孔,且使用的光刻胶与PI胶的解析度高于干膜,可以制作更小的线路。

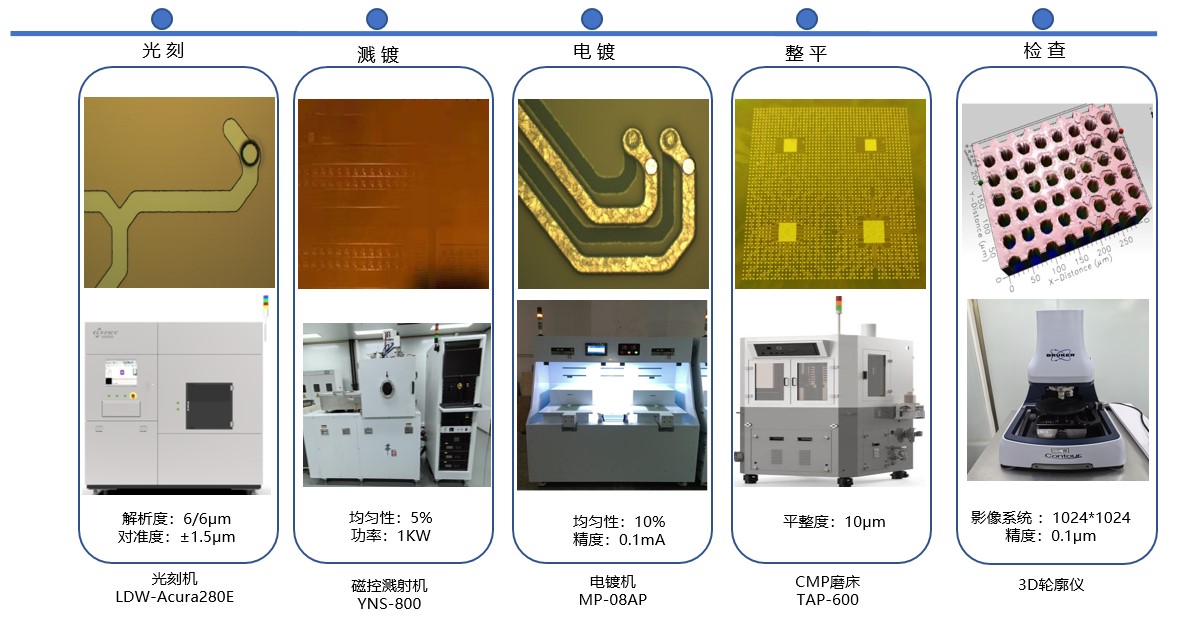

明阳中央实验室对RDL进行了深入的研究,建立了一条包含磁控溅射,光刻,匀胶显影,电镀蚀刻的试验线。

当前RDL技术已实现在硅基,陶瓷基,有机玻璃基板上的线路制作,可进行铜厚6-8μm,线宽线距8/10μm的二阶RDL制作,并已完成部分样品的制作与交付。

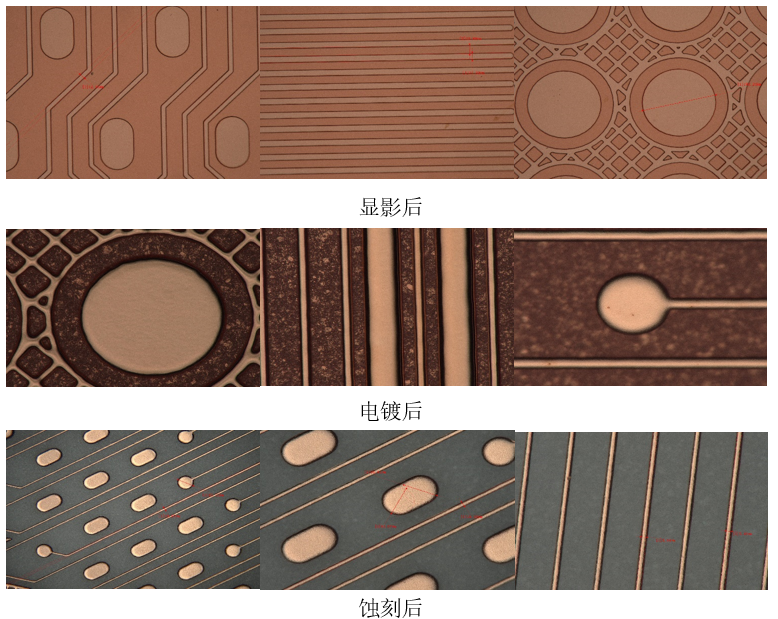

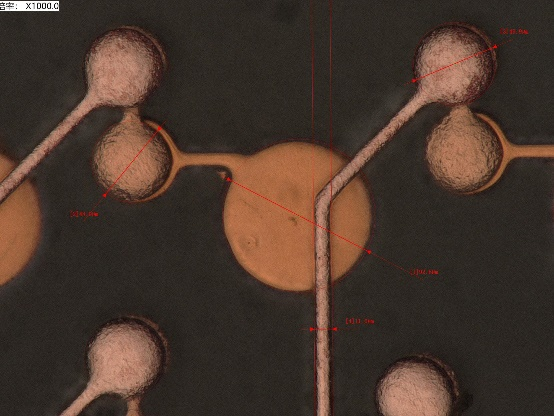

RDL工艺在显影后,电镀后,蚀刻后的过程图片,线路10μm

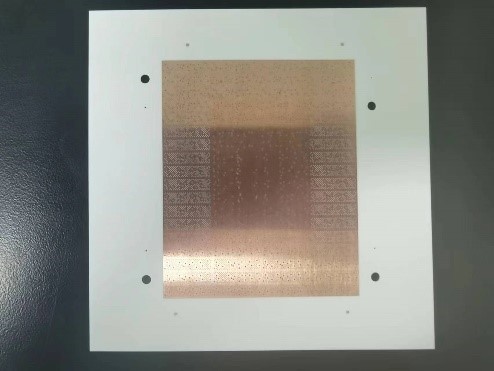

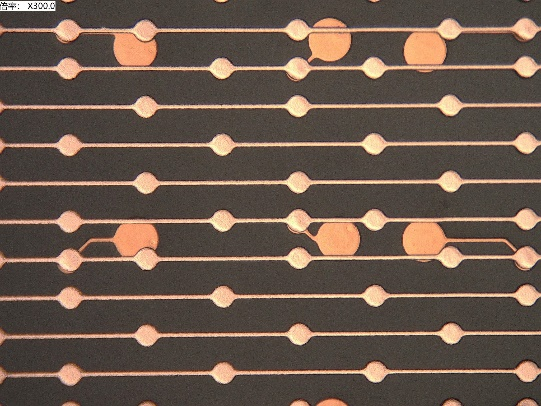

玻璃基板上的RDL,线宽线距25μm,表面处理镍钯金

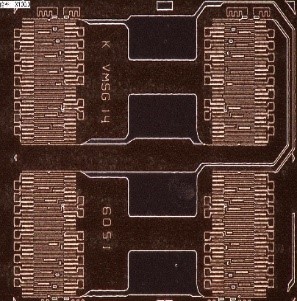

陶瓷基板上的RDL,双面图形,线宽线距25μm

有机基板上的RDL,线宽线距6/8μm,双面图形

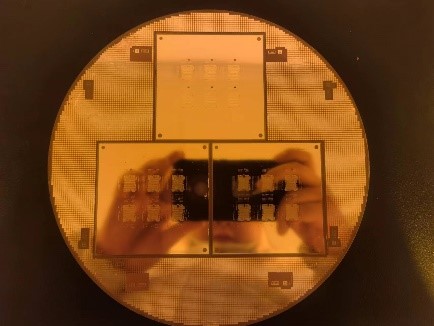

硅基板上的RDL,线宽线距10/10μm,pitch 85μm

玻璃基板上的三阶RDL,线宽线距10/10μm,pitch 85μm