一般情况下,当设计普通单、双面板时,无需考虑PCB的叠层问题,通常直接选择铜厚和板厚符合设计要求的覆铜板直接加工。但设计4层以上的PCB时,叠层设计直接影响PCB的性能和价格。

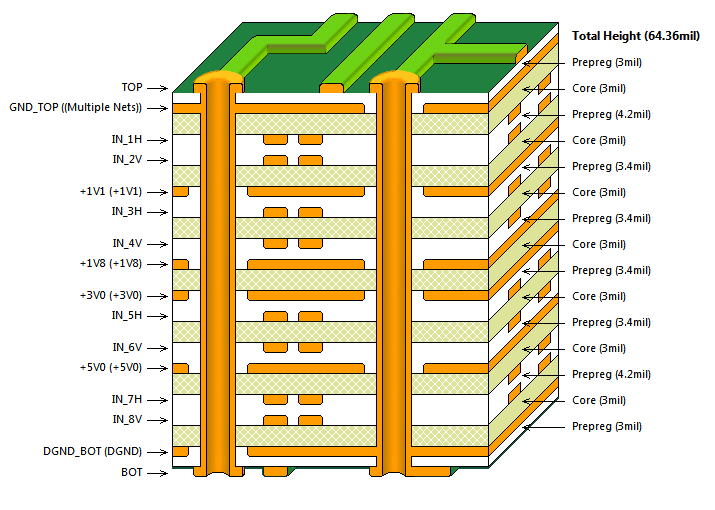

16层板的叠层设计

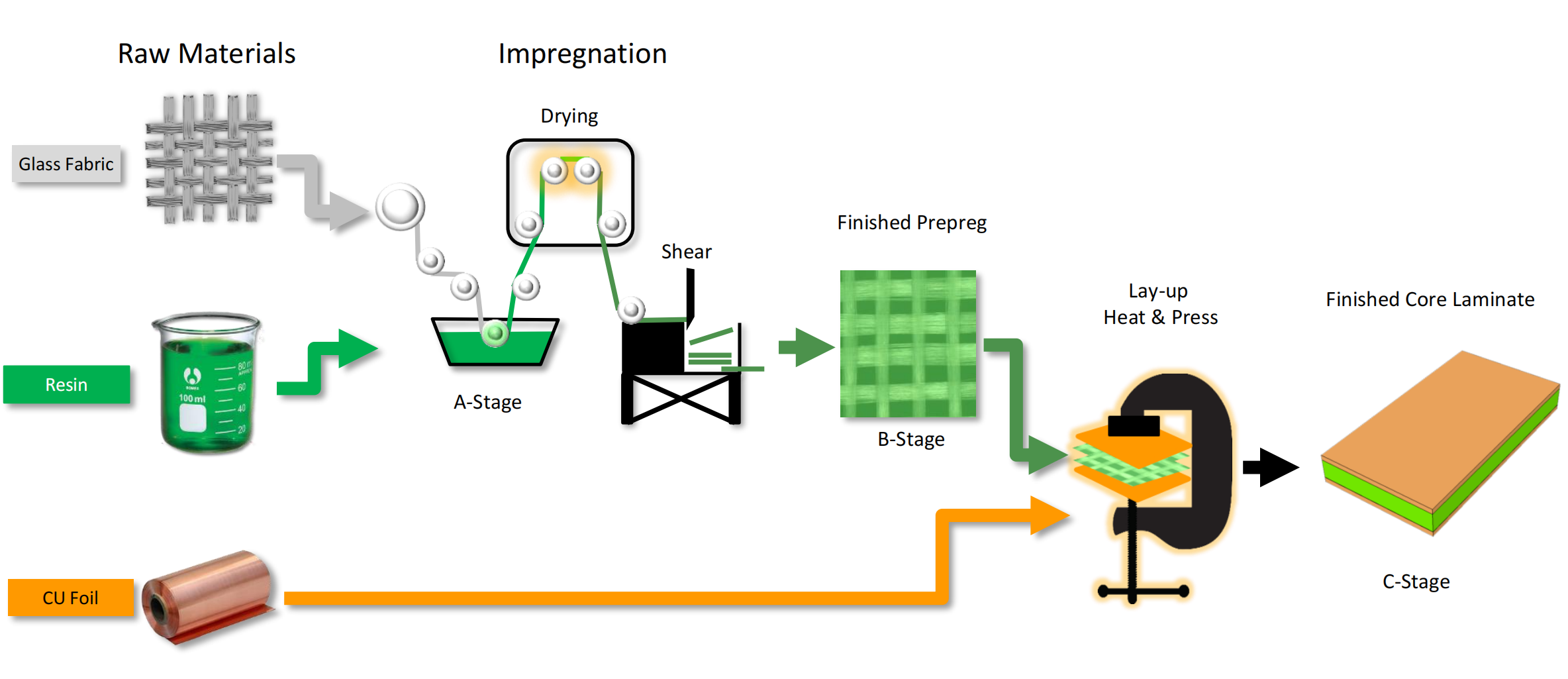

多层PCB由覆铜芯板(Core)、半固化片(prepreg,简称PP)与铜箔,一起按照叠层设计组合,经过压合制成。

在PCB开始设计之前,Layout工程师会根据电路板的尺寸、电路的规模和电磁兼容(EMC)的要求确定PCB的层数,然后确定元器件的布局,最后确认信号层、电源层和地层的划分。

PCB叠层需要从层数、信号类型、板厚、材料选择、铜厚、阻抗控制、EMI/EMC屏蔽、热管理、成本和可测试性等多方面考虑。

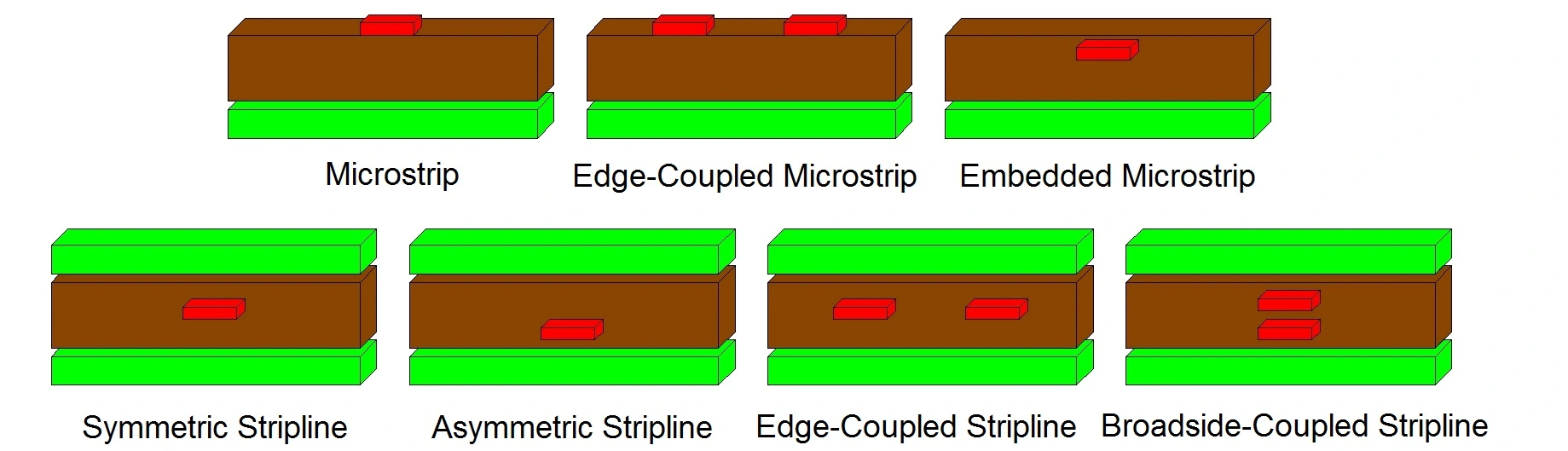

对于关键信号线,需要构建GND/Signal/GND的叠层组合,相邻信号层的带状线,交叉垂直布线,以最小化串扰耦合。从信号完整性的角度来讲,关键高速信号使用带状线(Stripline)布线,非关键高速信号可以选择使用微带线(Microstrip)布线。

如非必要,不建议使用宽边耦合带状线(Broadside-Coupled Stripline ),PCB加工过程中的曝光和蚀刻的偏移都会造成重叠错位,加工过程困难而且难以保证阻抗的一致性。

微带线和带状线布线的类型

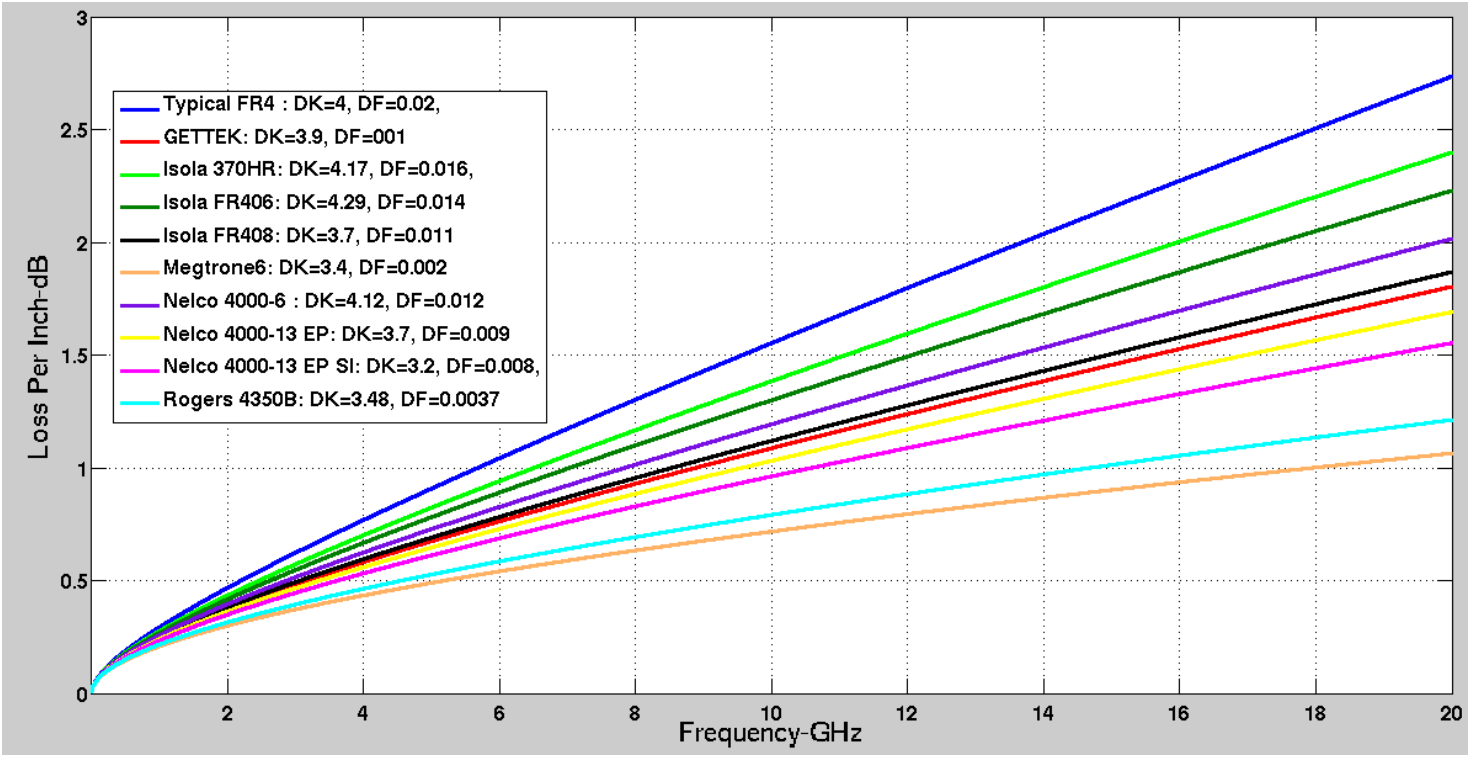

FR-4能够满足大多数PCB的需求,价格便宜而且电气性能良好,高速PCB会选用高速板材,比如松下的Megtron4/6等,射频PCB会选用 碳氢、Teflon或者陶瓷基板。如汽车灯板等对散热要求高的设计场景,会选用铝基或者铜基板材,在Mini LED等显示场景会使用玻璃基板材。

板材的关键性能指标如下:

高速PCB需要选择具有最低损耗角正切和较小介电常数的介电材料,高速PCB的设计需要特别注意材料明细,包括玻璃纤维(Fiberglass),电介质矩阵(Dielectric Matrix)和铜(Copper)。在较高数据速率下的信号具有较高的频率单元,波长更短,阻抗不连续会产生更多反射。需要考虑玻纤效应和铜箔表面粗糙度的影响。

不同型号板材对信号的衰减

在上图中,Typical FR4在28Gbps时每英寸有近2dB平均损耗(Nyquist为14GHz),Megtron6在相同频率只有0.85dB。

不同的玻纤对应的编织粗细不一样,开窗和交织的厚度也不一样,如果信号分别布在开窗上和玻纤上所表现的特性(阻抗、时延、损耗)也不一样(开窗和玻纤Dk/Df特性不一样导致的),这就是玻纤效应。

芯板(Core)的制造过程

玻纤布的类型

缓解玻纤效应的方法:

择最小化树脂窗口的玻纤类型材料;

使用Zig-Zag等10°走线方法;

在制板的时候让板厂旋转一定的角度;

使用扁平开纤玻布或者平织布。

铜箔粗糙度(铜牙)使线路的宽度、线间距不均匀,从而导致阻抗不可控,同时由于趋肤效应,电流集中在导体的表层,铜箔的表面粗糙度影响信号传输的长度。

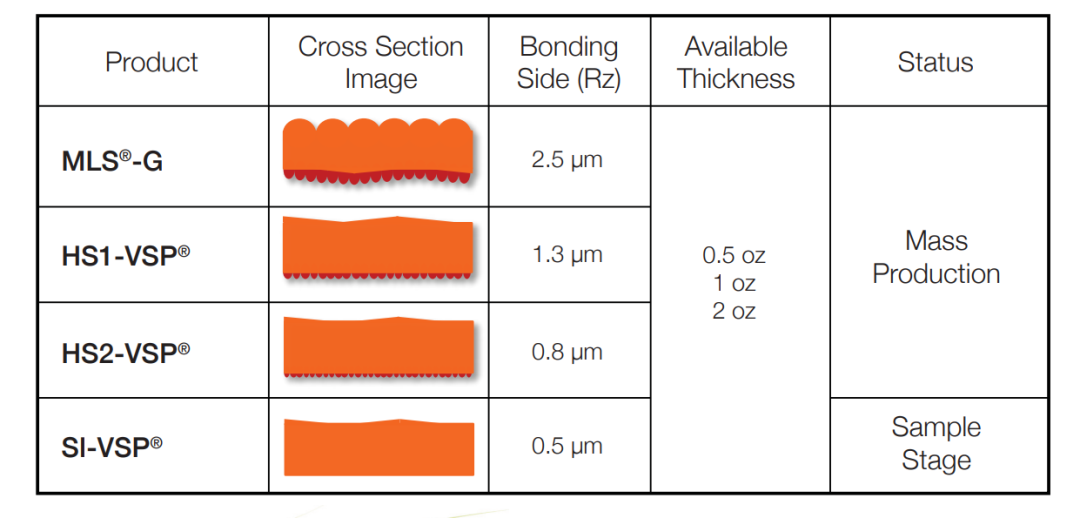

不同等级铜箔的表面粗糙度

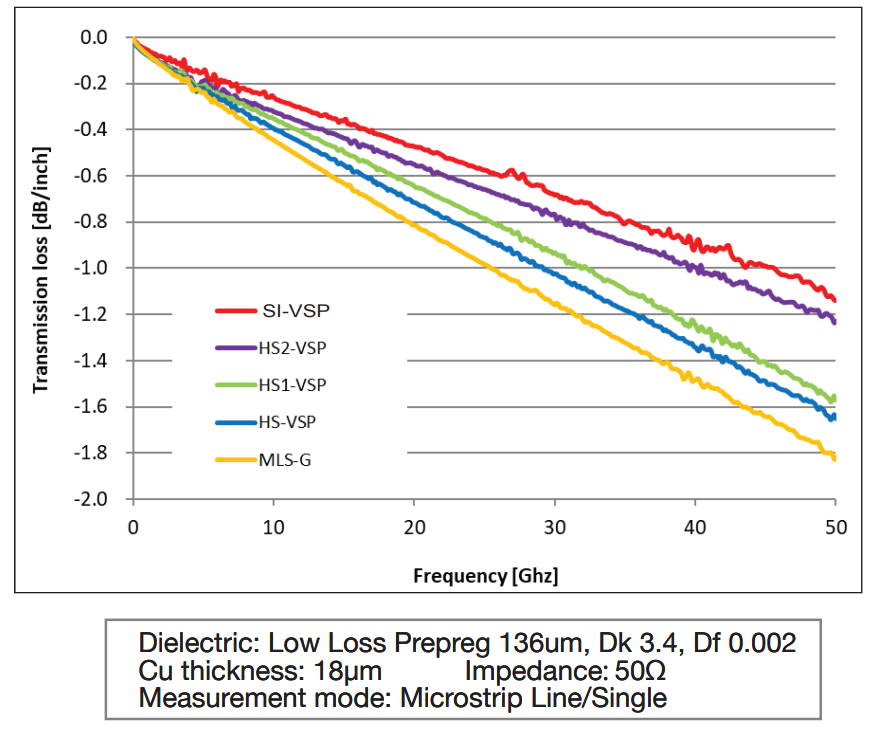

如下图所示,在5GHz以下铜箔粗糙度的影响不是太明显,大于5GHz铜箔粗糙度的影响开始越来越大,在大于10Ghz的高速信号的设计时尤其需要重视。

铜箔粗糙度对高速信号的衰减

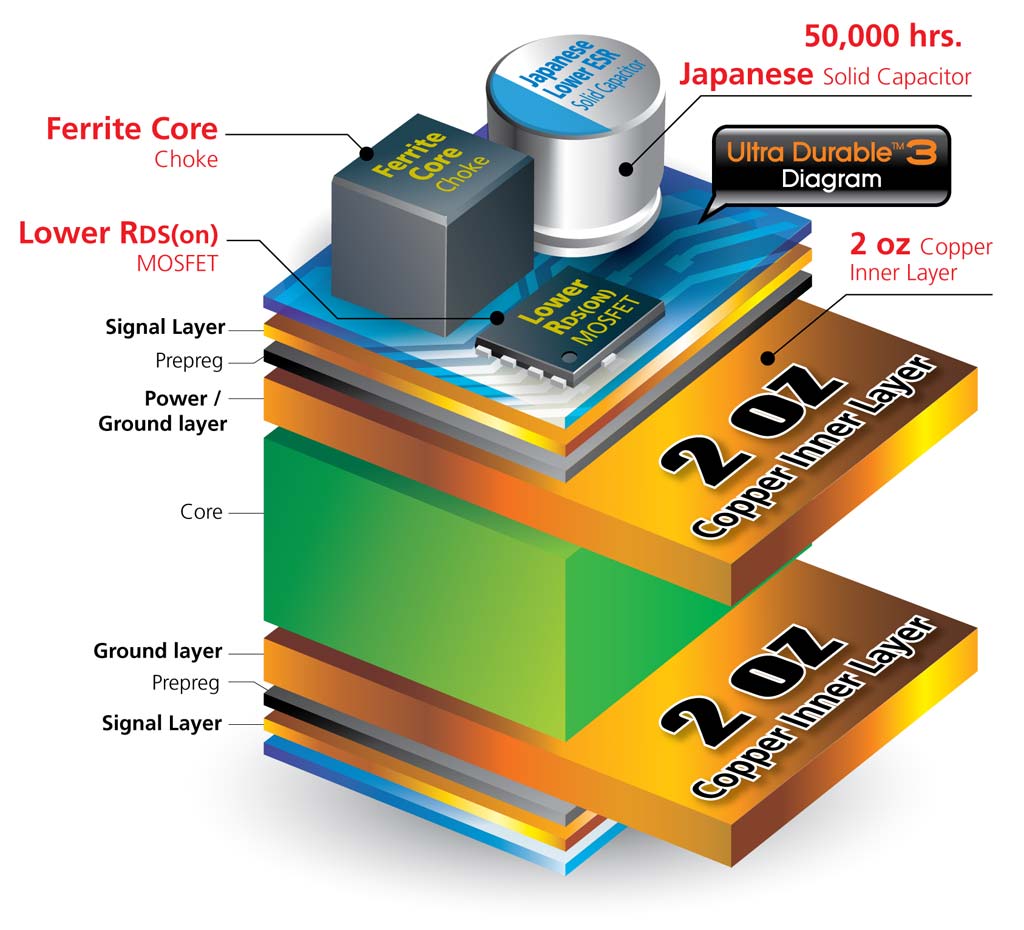

PCB铜箔的厚度以盎司(oz)为单位。常见的铜厚有三个尺寸,0.5oz(内层)、1oz(表层)和2oz,主要用在消费和通讯类产品上。3oz以上属于厚铜,常用于高压、大电流的电力电子产品。

电源板的叠层设计

叠层设计时必须平衡铜箔的厚度,使电源/地平面层铜的厚度满足载流要求。对于信号层铜的厚度来讲,线宽/线距较小,需要铜尽可能薄才能满足精确的蚀刻的要求。高速信号线由于趋肤效应的影响,电流只在铜箔表面附近流动,更厚的铜箔并不会带来更好的性能。所以内层信号层的铜厚通常为Hoz,即0.5盎司。

PCB上很多接口信号线都有阻抗要求,常见的单端50Ω、差分100Ω等。阻抗控制,需要有参考平面,一般需要四层以上。

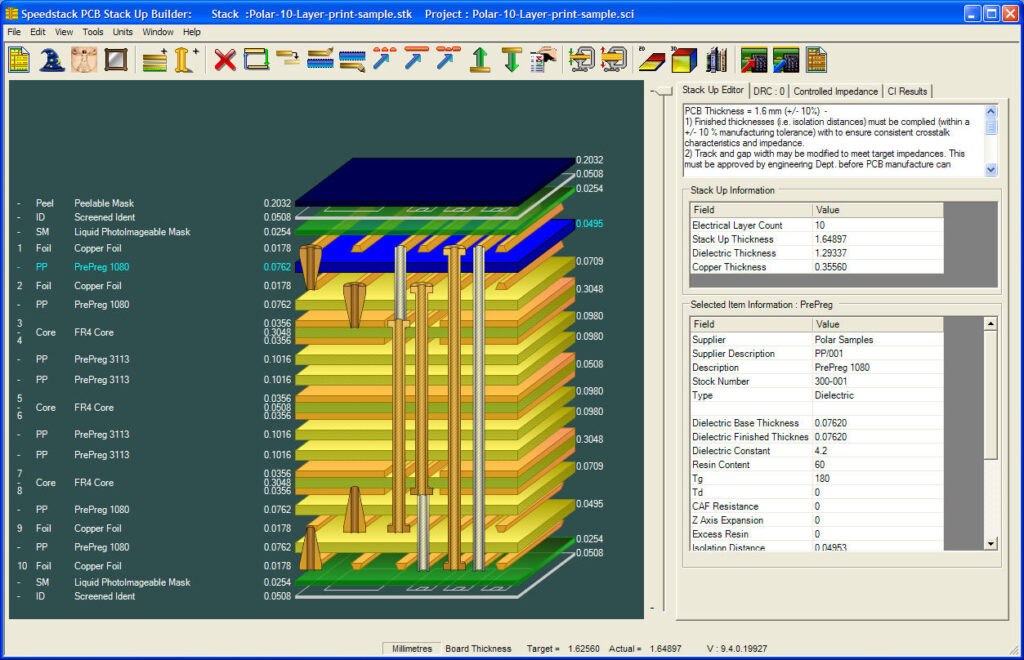

阻抗不匹配会导致信号失真、反射和辐射等信号完整性问题,影响PCB的性能。走线的铜厚、介电常数、线宽、线距都会影响阻抗。我们可以根据各种EDA工具去计算阻抗,然后按照设计的叠层结构,去调整走线的参数。目前常规的板厂都可以把阻抗控制在10%。

使用Polar来计算叠层阻抗

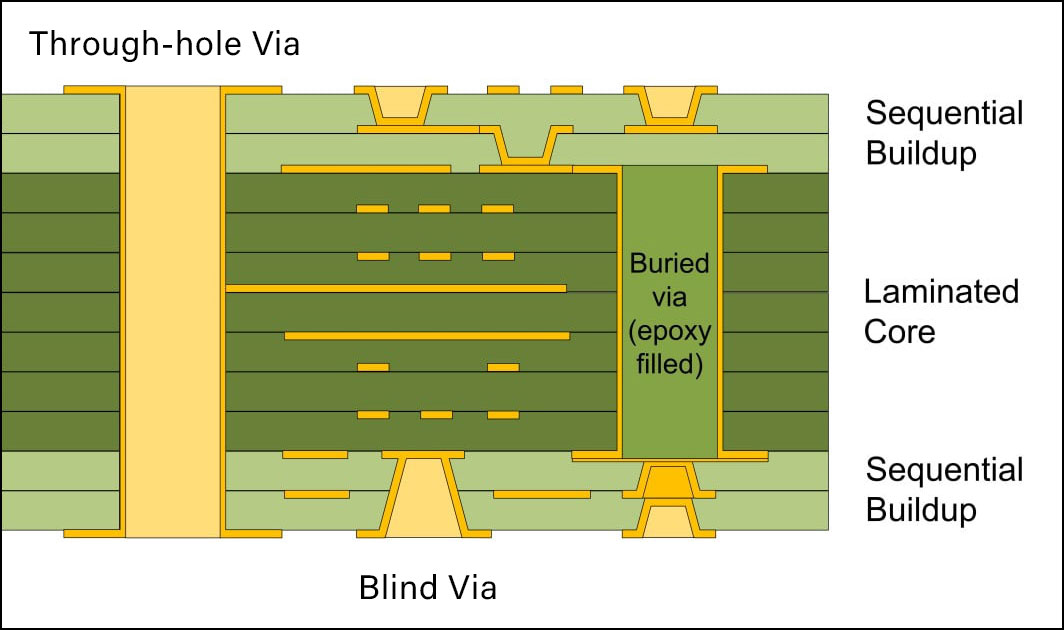

PCB中孔的类型

通孔(PTH)贯穿整个PCB可以连接所有层。盲孔(Blind Via)可以将外层连接至一个或多个内层,但不穿过PCB。埋孔(Buried Via)只连接PCB的内层。

高密度(HDI)PCB经常会使用盲孔和埋孔来优化布线空间,盲孔和埋孔也造成了PCB需要多次压合增加了工序,PCB的制造难度上升,因此也更加昂贵。

在叠层设计时,需要根据设计需要来设计整板的孔结构,在满足设计的前提下,尽量简化孔的结构。

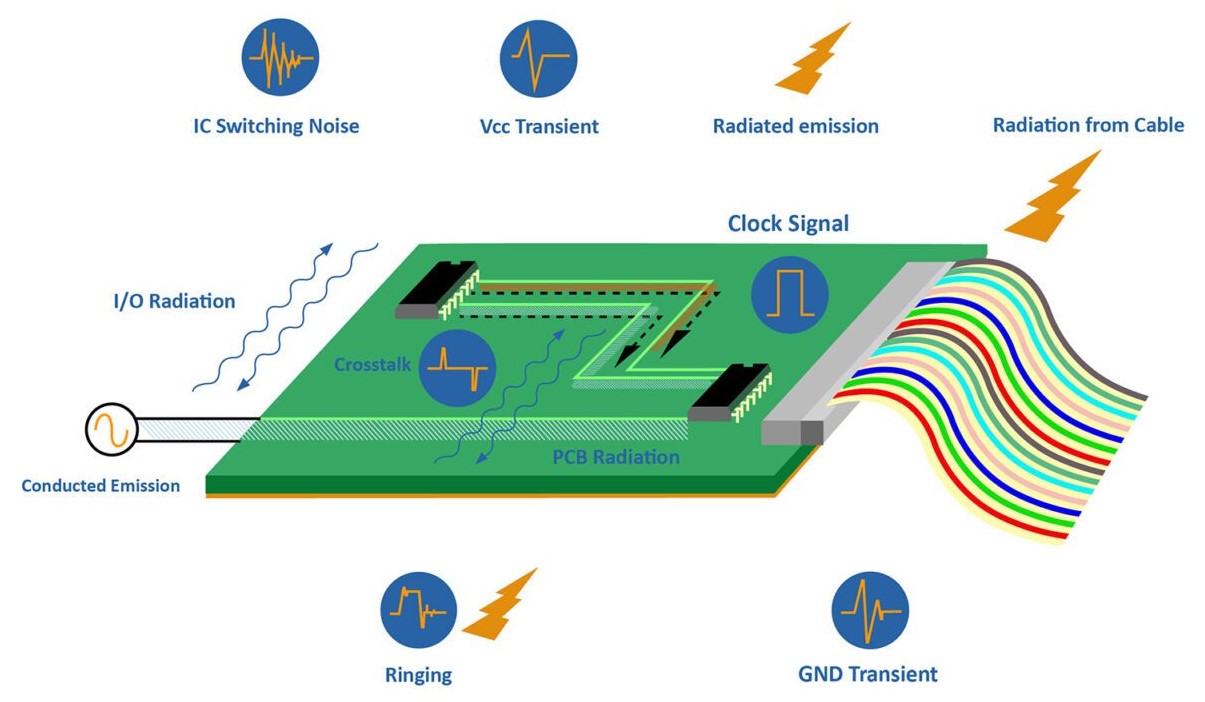

PCB叠层EMC设计时遵循以下原则:

板内电源平面和地平面尽量相互邻近,一般地平面在电源平面之上,这样的设计可以有效利用层间电容作为电源的平滑电容,同时接地平面对电源平面分布的辐射电流起到屏蔽作用。

电源和地层分配在内层,地平面可视为屏蔽层,可以很好地抑制电路板上固有的共模RF干扰,减小高频电源的分布阻抗。

布线层应尽量安排与电源或地平面相邻以产生通量对消作用。

PCB板上的辐射

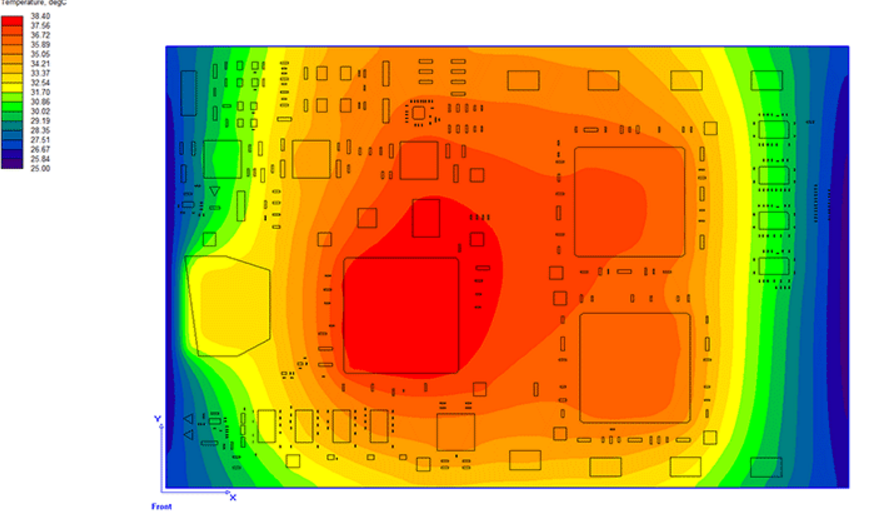

PCB叠层设计需要考虑热管理,保证元器件散发的热量有效传导出去,防止热损坏提高电路可靠性。在设计流程中,我们会先根据元器件功耗进行热仿真,根据仿真结果优化元器件布局和设计相应的散热方案。

在叠层设计阶段,也可以针对性做散热设计:

优先选择导热系数高的板材,按需选择金属基板;

大功率器件下方设计散热焊盘,使用散热孔;

埋铜块,嵌铜柱,提高热传导效率;

增加地平面,空白区域铺地,增大散热面积。

板级热仿真

常规的PCB成品厚度为0.5mm、0.8mm、1.0mm、1.2mm、1.6mm、2.0mm、3.2mm、6.4mm等等。一般面积小的板厚相对较薄,经常插拔、安装应力较大、面积大的板子,从结构可靠性角度需要做厚一些。

PCB叠层设计一般遵循以下步骤:

1.确定层叠的总厚度,即板厚;

2.确定PCB层数,并分配信号层、地平面层和电源层;

3.确定内层和外层的铜厚;

4.确定阻抗线的分布;

5.确定过孔结构;

6.确定每层的残铜率,最好要对称;

7.选择满足设计要求的板材、PP和铜箔材料。

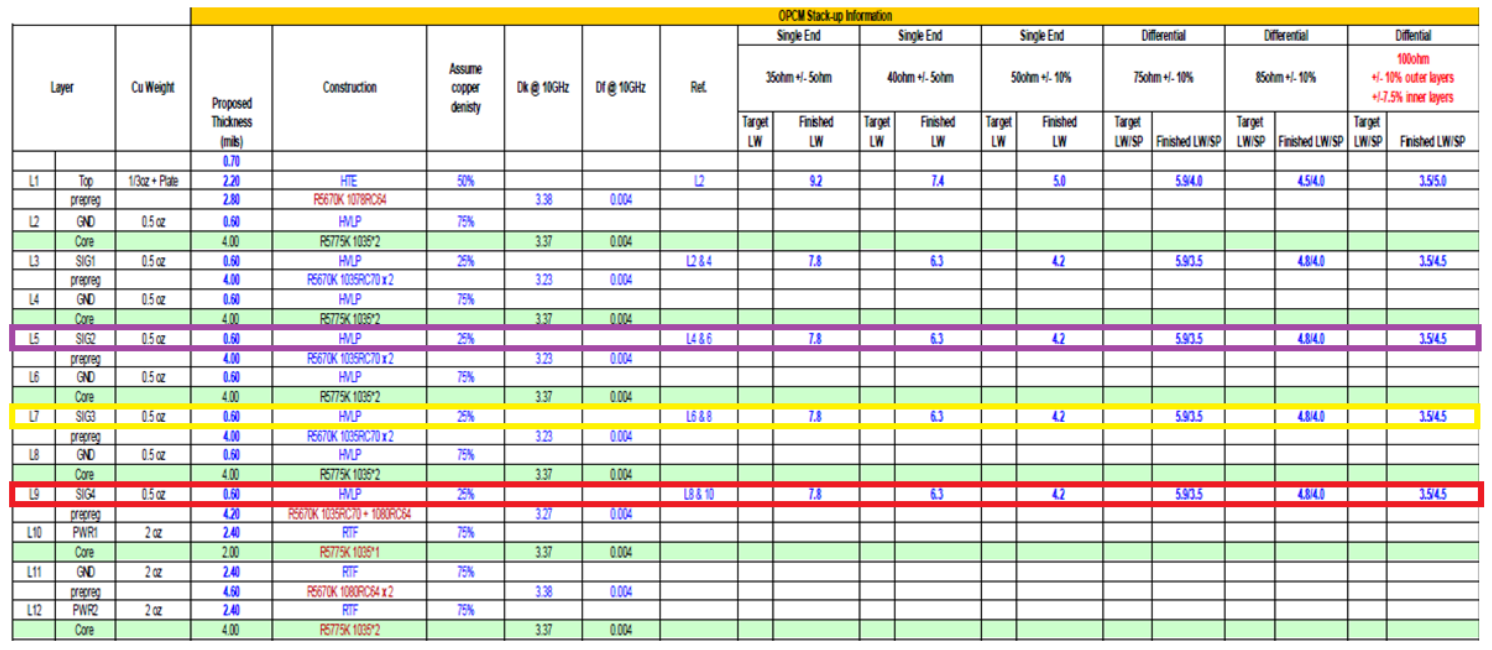

以12层板为例,设计好的叠层结构如下:

声明:文章内容整理自网络公开素材, 版权归原作者平台所有,仅用于信息分享,如有侵权请联系删除。